# High Input Impedance Voltage-Mode Universal Biquadratic Filter with One Input and Five Outputs using plus-type DDCCs

Jitendra Mohan

Department of Electronics & Communication Engineering, Jaypee Institute of Information Technology, Noida (INDIA) Girish Garg

Department of Electronics and Communication Engineering, Jaypee University of Information Technology, Waknaghat, Solan (INDIA)

Durg Singh Chauhan Department of Electrical Engineering, Institute of Technology, Banaras Hindu University, Varanasi-221005 (INDIA)

Abstract—This paper presents a voltage mode universal biquadratic filter with one input and five output terminals, realizing all the standard filter functions that are high pass, band pass, low pass, notch and all pass, without changing the circuit topology. The proposed circuit employs three plus-type differential difference current conveyors (DDCCs), three grounded resistors and two grounded capacitors. The proposed filter enjoys the features of high input impedance and low active and passive sensitivities. PSPICE simulation results are given to confirm the validity of the proposed circuit.

Keywords— active filter, high input impedance, analogue circuits, current conveyors.

## I. INTRODUCTION

A simple yet useful analog circuit function so often required in communication measurement, and instrumentation system is a biquadratic filter, since it can provide all the standard functions in the same topology [1-2]. There has been a great attention on the design and study of biquadratic analog filter using different current-mode active elements [3]. Voltage mode (VM) biquadratic filter with high input impedance are of great interest because several cells of this kind can be directly connected to implement higher order filters without requiring any other circuitry [8, 13-16, 18-21].

With the increasing interest on the voltage mode universal biquadratic filter with single input and five outputs [7, 11-12, 14-15, 19], there is still need to develop new universal biquadratic filters that offer new advantages. In literature there exist several biquadratic filters based on different active elements [4-21] however; these reported circuits suffer from at least one of the following drawbacks:

- Low-input impedance [4-7, 9, 11-12, 17]

- Excessive use of passive components. [4-5, 7, 13]

- Use of floating capacitor or resistors. [5-8, 11-12, 14-15, 19-20]

- Cannot provide simultaneous, high pass (HP), band pass (BP), low pass (LP), notch (NH) and all-pass (AP) filters. [4, 6, 8-10, 13, 16-18, 20-21]

The literature shows that none of the recently reported works provide all the above features simultaneously. Most of the circuits offer high input impedance and realizes all the standard functions simultaneously from the same topology but one/more passive elements are floating [14, 15, 19]. Recently published circuits in [20] presents cascadable notch/all-pass filters with a feature of high-input impedance and low-output impedances by employing two plus-type differential difference current conveyors [22], two resistors and two grounded capacitors. However it realizes only two standard filter functions.

In this paper, a voltage mode universal biquadratic filter with single input and five output using three plus-type differential difference current conveyor (DDCC+s), three grounded resistors and two grounded capacitors is presented. Moreover, the circuit enjoys high input impedance so that it can be directly connected in cascade to implement higher order filters. With respect to one input and five output circuits in [7, 11-12, 14-15, 19] the proposed circuit employs only grounded passive components, which make it suitable for integrated circuit (IC) implementation and also cancel the effect of parasitic impedances of the active element [23].

## II. THE PROPOSED CIRCUIT

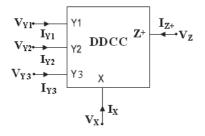

The symbol of the DDCC+ is shown in Figure 1, is a five terminal active element, which can be represented by the following matrix equation [22]:

Proc. of the Intl. Conf. on Advances in Electronics, Electrical and Computer Science Engineering — EEC 2012 Edited by Dr. R. K. Singh. Copyright © Institute of Research Engineers and Doctors. All rights reserved. ISBN: 978-981-07-2950-9

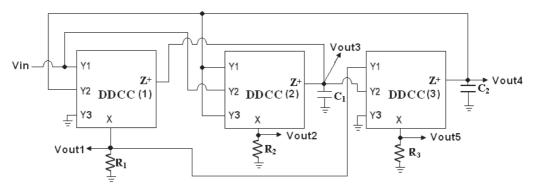

Figure 2. Proposed VM Universal biquadratic filter.

Figure 1. Symbol of DDCC+.

where the suffixes refer to the respective terminals. The voltage at X-terminal follows the voltage difference and addition of terminal Y1, Y2, Y3. The current at terminal Z follow the current at terminal X. It is shown that the ideal DDCC+ exhibits an infinite input resistance at the Y1, Y2, and Y3 terminals. The X-terminal exhibit zero resistance and the Z-terminal exhibit an infinite resistance.

The proposed circuit is shown in Figure 2 by employing three DDCC+s, three grounded resistors and two grounded capacitors. The use of grounded passive components is particularly attractive from the point of IC implementation [23]. A routine analysis of the circuit of Figure 2 yields the following filter transfer functions

$$\frac{V_{OUT1}}{V_{IN}} = \frac{s^2 + \frac{1}{C_1 C_2 R_2 R_3}}{s^2 + \frac{1}{C_2 R_3} s + \frac{(2R_1 - R_2)}{C_1 C_2 R_1 R_2 R_3}}$$

(2)

$$\frac{V_{OUT2}}{V_{IN}} = -\left(\frac{s^2 - \frac{1}{C_2 R_3}s + \frac{1}{C_1 C_2 R_1 R_3}}{s^2 + \frac{1}{C_2 R_3}s + \frac{(2R_1 - R_2)}{C_1 C_2 R_1 R_2 R_3}}\right)$$

(3)

$$\frac{V_{OUT3}}{V_{IN}} = \frac{\frac{1}{C_1 C_2 R_2 R_3} + \frac{(R_1 - R_2)}{C_1 R_1 R_2} s}{s^2 + \frac{1}{C_2 R_3} s + \frac{(2R_1 - R_2)}{C_1 C_2 R_1 R_2 R_3}}$$

(4)

$$\frac{V_{OUT4}}{V_{IN}} = \frac{\frac{1}{C_2 R_3} s + \frac{(R_1 - R_2)}{C_1 C_2 R_1 R_2 R_3}}{s^2 + \frac{1}{C_2 R_3} s + \frac{(2R_1 - R_2)}{C_1 C_2 R_1 R_2 R_3}}$$

(5)

( D

D )

$$\frac{V_{OUT5}}{V_{IN}} = \frac{s^2 + \frac{(R_1 - R_2)}{C_1 R_1 R_2}s}{s^2 + \frac{1}{C_2 R_3}s + \frac{(2R_1 - R_2)}{C_1 C_2 R_1 R_2 R_3}}$$

(6)

For  $R_1 = R_2 = R$ , the equations from (2)-(6) becomes

$$\frac{V_{OUT1}}{V_{IN}} = \frac{s^2 + \frac{1}{C_1 C_2 R R_3}}{s^2 + \frac{1}{C_2 R_3} s + \frac{1}{C_1 C_2 R R_3}}$$

(7)

$$\frac{V_{OUT2}}{V_{IN}} = -\left(\frac{s^2 - \frac{1}{C_2 R_3}s + \frac{1}{C_1 C_2 R R_3}}{s^2 + \frac{1}{C_2 R_3}s + \frac{1}{C_1 C_2 R R_3}}\right)$$

(8)

$$\frac{V_{OUT3}}{V_{IN}} = \frac{\frac{1}{C_1 C_2 R R_3}}{s^2 + \frac{1}{C_2 R_3} s + \frac{1}{C_1 C_2 R R_3}}$$

(9)

$$\frac{V_{OUT4}}{V_{IN}} = \frac{\frac{1}{C_2 R_3} s}{s^2 + \frac{1}{C_2 R_2} s + \frac{1}{C_1 C_2 R_2}}$$

(10)

1

$$\frac{V_{OUT5}}{V_{IN}} = \frac{s^2}{s^2 + \frac{1}{C_2 R_3} s + \frac{1}{C_1 C_2 R R_3}}$$

(11)

From (7)-(11), it can be seen that a notch (NH) response is obtained from  $V_{\rm OUT1}$ , a all-pass(AP) response is obtained from  $V_{\rm OUT2}$ , a low-pass (LP) response is obtained from  $V_{\rm OUT3}$ , a band-pass (BP) response is obtained from  $V_{\rm OUT4}$ , and an high-pass (HP) response is obtained from  $V_{\rm OUT5}$ . In all cases, the resonance angular frequency  $\omega_{\rm o}$ , the quality factor Q and the bandwidth  $\omega_{\rm o}/Q$  are given by

$$\omega_{o} = \left(\frac{1}{C_1 C_2 R R_3}\right)^{\frac{1}{2}}$$

(12)

$$Q = \left(\frac{R_3 C_2}{R C_1}\right)^{\frac{1}{2}} \tag{13}$$

$$\frac{\omega_o}{Q} = \frac{1}{R_3 C_2} \tag{14}$$

The input voltage is connected simultaneously to the high input impedance terminals Y1 and Y2 of the DDCC+(1) and DDCC+(2), respectively. So the circuit enjoys the feature of high input impedance. Therefore, it can be used in cascade for realizing higher order filters.

Note that the proposed circuit employs two grounded capacitors at the Z-terminals and three grounded resistors at the X-terminal of the DDCC+. So this circuit offers the feature of direct incorporation of the shunt parasitic capacitance and the series parasitic resistance as a part of the main capacitance and resistance at the Z and X terminals, respectively.

#### III. NON-IDEAL ANALYSIS

Taking into consideration the DDCC+ non idealities, the relationship of the terminal voltages and current can be rewritten as

where  $\beta_{kj} = (1 - \varepsilon_{kj})$ , for j = 1, 2, 3 and  $\alpha_{kl} = (1 - \delta_{kl})$ . Also,  $\varepsilon_{kj}$ and  $\delta_{kl}$  ( $|\varepsilon_{kj}| << 1$  and ( $|\delta_{kl}| << 1$ ) represents voltage tracking error and current tracking error of the DDCC+.  $\beta_{kl}$ ,  $\beta_{k2}$ ,  $\beta_{k3}$ , are the voltage transfer gain and  $\alpha_{kl}$  is the current transfer gain of *the k*-th DDCC+ (k = 1,2,3). Reanalysis of the circuit in Figure 2 that the denominator of the voltage transfer functions becomes

$$D(s) = s^{2} + \frac{\beta_{12}\beta_{31}\alpha_{31}}{C_{2}R_{3}}s + \frac{\beta_{12}\beta_{32}\alpha_{31}\left[\left(\beta_{21} + \beta_{23}\right)\alpha_{21} - \alpha_{11}\right]}{C_{1}C_{2}RR_{3}}$$

(16)

The non-ideal  $\omega_0$ , Q and  $\omega_0$ , Q are given by

$$\omega_{0} = \left(\frac{\beta_{12}\beta_{32}\alpha_{31}\left[\left(\beta_{21} + \beta_{23}\right)\alpha_{21} - \alpha_{11}\right]}{C_{1}C_{2}RR_{3}}\right)^{\frac{1}{2}}$$

(17)

$$Q = \frac{1}{\beta_{31}} \left( \frac{\beta_{32} \left[ \left( \beta_{21} + \beta_{23} \right) \alpha_{21} - \alpha_{11} \right] C_2 R_3}{\beta_{12} \alpha_{31} C_1 R} \right)^{\frac{1}{2}}$$

(18)

$$\frac{\omega_o}{Q} = \frac{\beta_{12}\beta_{31}\alpha_{31}}{C_2R_3}$$

(19)

The active and passive sensitivities of the proposed SIMO voltage-mode filter are derived from eqns. (11)-(12). These are as follows:

$$S_{C_{1},C_{2},R,R_{3}}^{\omega_{o}} = -S_{\beta_{12},\beta_{32},\alpha_{31}}^{\omega_{o}} = -\frac{1}{2},$$

$$S_{C_{1},R}^{Q} = -S_{C_{2},R_{3}}^{Q} = S_{\beta_{12},\alpha_{31}}^{Q} = -S_{\beta_{32}}^{Q} = -\frac{1}{2}, S_{\beta_{13}}^{Q} = -1,$$

$$S_{\alpha_{11}}^{\omega_{o}} = S_{\alpha_{21}}^{Q} = \frac{1}{2} \frac{\alpha_{11}}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\alpha_{21}}^{\omega_{o}} = S_{\alpha_{21}}^{Q} = -\frac{1}{2} \frac{\alpha_{21}\left(\beta_{21} + \beta_{23}\right)}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\beta_{21}}^{\omega_{o}} = S_{\beta_{21}}^{Q} = -\frac{1}{2} \frac{\alpha_{21}\beta_{21}}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\beta_{23}}^{\omega_{o}} = S_{\beta_{23}}^{Q} = -\frac{1}{2} \frac{\alpha_{21}\beta_{23}}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\beta_{23}}^{\omega_{o}} = S_{\beta_{23}}^{Q} = -\frac{1}{2} \frac{\alpha_{21}\beta_{23}}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\beta_{23}}^{\omega_{o}} = -\frac{1}{2} \frac{\alpha_{21}\beta_{23}}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\beta_{23}}^{\omega_{o}} = -\frac{1}{2} \frac{\alpha_{23}\beta_{23}}{\left[\alpha_{11} - \alpha_{21}\left(\beta_{21} + \beta_{23}\right)\right]},$$

$$S_{\beta_{23}}^{\omega_{o}} = -\frac{1}{2} \frac{\alpha_{23}\beta_{23}}{\left[\alpha_{23} - \beta_{23}\right]},$$

$$S_{\beta_{23}}^{$$

From the above sensitivity results it is evident that the sensitivities are low and within unity in absolute value.

## IV. SIMULATION RESULTS

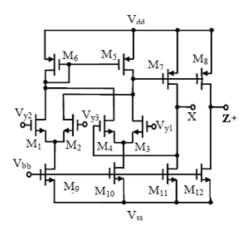

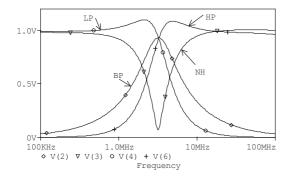

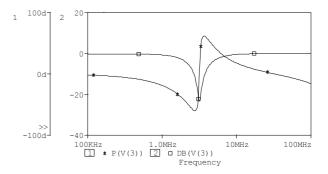

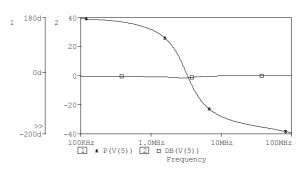

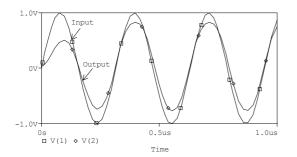

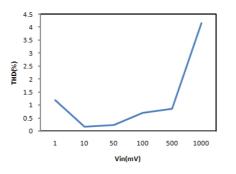

To verify the theoretical study, the proposed universal biquadratic filter is simulated by using the PSPICE. The DDCC+ was realized by the CMOS implementation in Figure 3 [24] using 0.5µm, level 3 MOSFET parameters as listed in Table I.The aspect ratio of the MOS transistor are listed in Table II, with the following DC biasing levels  $V_{dd} = -V_{ss} =$ 2.5V and  $V_{bb} = 1.2$  V. The proposed circuit is designed for  $R_1$  $= R_2 = R_3 = 5 \text{ k}\Omega$ ,  $C_1 = C_2 = 10 \text{ pf}$  with the pole frequency of  $f_0 = 3.17$  MHz and a quality factor of Q = 1. The magnitude responses of LP, HP, BP and NH are shown in Figure 4. Figure 5 and Figure 6 shows the magnitude and phase responses of NH and AP of Figure 2. The signal behavior of the proposed circuit is investigated by applying a sinusoidal input voltage with amplitude of 2 V peak-to-peak at a frequency of 3.17 MHz. The time domain input and output signal of the BP response of the proposed circuit is shown in Figure 7. The total harmonic distortion of the output signal at the BP response is shown in Figure 8. The THD is found to be within 5% for a sinusoidal input signal with 2V peak to peak.

Figure 3. CMOS implementation of DDCC+. [24].

Figure 4. Simulated magnitude responses of the LP, BP, HP, NH at 3.17 MHz of Figure 2.

Table I. 0.5µm LEVEL 3 MOSFET PARAMETERS

| NMOS:                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEVEL = 3 UO = 460.5 TOX = 1.0E-8 TPG=-1<br>VTO = .62 JS = 1.8E-6 XJ = .15E-6 RS = 417 RSH<br>= 2.73 LD = 0.04E-6 ETA = 0 VMAX = 130E3<br>NSUB = 1.71E17 PB = .761 PHI = 0.905 +THETA<br>= 0.129 GAMMA = 0.69 KAPPA = 0.1 AF =1<br>WD= .11E-6 CJ = 76.4E-5 MJ = 0.357 CJSW =<br>5.68E-10 MJSW = 0.302 CGSO = 1.38E-10<br>CGDO = 1.38E-10 CGBO = 3.45E-10 KF = 3.07E-<br>28 DELTA = 0.42 NFS = 1.2E11 |

| PMOS:                                                                                                                                                                                                                                                                                                                                                                                                |

| LEVEL = 3 UO = 100 TOX = 1E-8 TPG = 1 VTO<br>=58 JS = .38E-6 XJ = 0.1E-6 RS = 886 RSH =<br>1.81 LD = 0.03E-6 ETA = 0 VMAX = 113E3<br>NSUB = 2.08E17 PB = .911 PHI = 0.905 THETA<br>= 0.120 GAMMA = .76 KAPPA = 2 AF = 1 WD =<br>.14E-6 CJ = 85E-5 MJ = 0.429 CJSW = 4.67E-10<br>MJSW = 0.631 CGSO = 1.38E-10 CGDO = 1.38E-<br>10 CGBO = 3.45E-10 KF = 1.08E-29 DELTA =<br>0.81 NFS = 0.52E11         |

Table II. DEVICE DIMENSIONS USED IN SIMULATION

| Transistors                                                          | W/L   |

|----------------------------------------------------------------------|-------|

| M <sub>1</sub> , M <sub>2</sub> , M <sub>3</sub> , M <sub>4</sub>    | 1.6/1 |

| M <sub>5</sub> , M <sub>6</sub>                                      | 8/1   |

| M <sub>7</sub> , M <sub>8</sub> ,                                    | 90/1  |

| M <sub>9</sub> , M <sub>10</sub> , M <sub>11</sub> , M <sub>12</sub> | 20/1  |

Figure 5. Simulated magnitude and phase response of the NH at 3.17 MHz of Figure 2.

Figure 6. Simulated magnitude and phase response of the AP at 3.17 MHz of Figure 2.

Figure 7 Input and Output signal of the BP response at 3.17 MHz of Figure 2.

Figure 8 THD variation of the BP response against input voltage at 3.17 MHz.

# V. CONCLUSION

In this paper, a high-input impedance voltage-mode universal biquadratic filter with single input and five outputs is presented. The proposed circuit uses three plus-type differential difference current conveyors, two grounded capacitors and three grounded resistors. All the standard filter responses are obtained without changing the passive element. Also the circuit offers the direct incorporation of shunt parasitic capacitances and series parasitic resistances of the DDCC+ as a part of main capacitances and resistances, low active and passive sensitivities and high-input impedance for voltage-mode cascadability.

### REFERENCES

- R. Schaumann and M. E. Van Valkenburg, "Design of Analog Filters" Oxford Press, 2006.

- [2] M. A. Ibrahim, S. Minaei and H. Kuntman, "A 22.5 MHz current-mode KHN-biquad using differential voltage current conveyor and grounded passive elements" International Journal of Electronics and Communications, vol. 59, pp. 311-318, 2005.

- [3] B. Wilson, "Recent developments in current conveyor and current-mode circuits" IEE proceedings- Circuits Devices and Systems, vol. 137, pp. 63-77, 1990.

- [4] A. M. Soliman, "Kerwin–Huelsman–Newcomb circuit using current conveyors" Electronics Letters, vol. 30, pp. 2019-2020, 1994.

- [5] M. Higashimura and Y. Fukui, "Universal filter using plus-type CCIIs" Electronics Letter, vol. 32, pp. 810-811, 1996.

- [6] S. I. Liu and J. L. Lee, "Voltage-mode universal filters using two current conveyors" International Journal of Electronics, vol. 82, pp. 145-150, 1997.

- [7] M. T. Abuelmaatti and H. A. Al-Zaher, "New universal filter with one input and five outputs using current-feedback amplifiers" Analog Integrated Circuits and Signal Processing, vol. 16, pp. 239-244,1998.

- [8] J. W. Horng, "High-input impedance voltage-mode universal biquadratic filter using three plus-type CCIIs" IEEE Transactions on Circuits and Systems-II, vol. 48, no. 10, pp. 996-997, 2001.

- [9] J. W. Horng, W. Y. Chiu and H. Y. Wei, "Voltage-mode high-pass, band-pass and low pass filters using two DDCCs" International Journal of Electronics, vol. 91, no.8, pp. 461-464, 2004.

- [10] M. A. Ibrahim, H. Kuntman, and O. Cicekoglu, Single DDCC biquads with high input impedance and minimum number of passive elements, Analog Integrated Circuits and Signal Processing, vol. 43 pp. 71–79, 2005.

- [11] H. P. Chen, "Universal voltage-mode filters using only plus-type DDCCs" Analog Integrated Circuits and Signal Processing, vol. 50, pp. 137-139, 2007.

- [12] H. P. Chen and S.S. Shen, "A versatile universal capacitor-grounded voltage-mode filter using DVCCs" ETRI Journal, vol. 29, pp. 470-476, 2007.

- [13] W. Y. Chiu and J.W. Horng, "High-input and low-output impedance voltage-mode universal biquadratic filter using DDCCs" IEEE Transactions on Circuits and Systems-II, Express Briefs, vol. 54, no.8, pp. 649-652, 2007.

- [14] W. Y. Chiu, J. W. Horng and S. T. Cheng, "Universal filter with one input and five outputs using DDCCs" International symposium on intelligent signal processing and communication system (ISPACS), 2008.

- [15] W. Y. Chiu, J. W. Horng and S. S. Yang, "High-input impedance voltage-mode universal biquadratic filter with one input and five outputs using DDCCs" 4th IEEE International Symposium on Electronic Design, Test and Application, pp. 346-350, 2008.

- [16] S. Minaei and M.A. Ibrahim, "A mixed-mode KHN-biquad using DVCC and grounded passive elements suitable for direct cascading" International Journal of Circuit Theory and Application, vol. 37, no. 7, pp. 793-810, 2009.

- [17] S. Maheshwari, "High performance voltage-mode multifunction filter with minimum component count" WSEAS Transactions on Electronics, vol. 5, no. 6, pp. 244-249, June.2008.

- [18] J. W. Horng "High input impedance voltage mode universal biquadratic filter with three inputs using DDCCs" Circuits Systems and Signal Processing, Vol. 27, pp. 553-562, 2008.

- [19] S. Maheshwari, J. Mohan, D. S. Chauhan, "High input impedance voltage-mode universal filter and quadrature oscillator" Journal of Circuits, Systems, and Computers, vol. 19, pp. 1597-1607, 2010.

- [20] S. Maheshwari, J. Mohan, D. S. Chauhan, "Cascadable all-pass and notch filter configurations employing two plus-type DDCCs" Journal of Circuits, Systems, and Computers, vol. 20, pp. 329-347, 2011.

- [21] S. Siripongdee and W. Mekhum, "A design of electronically tunable voltage mode universal filter with high input" International Journal of Electronics and Electrical Engineering, vol. 6, 2012.

- [22] W. Chiu, S.I. Liu, H.W. Tsao and J. J. Chen, "CMOS differential difference current conveyors and their applications" IEE proceedings-Circuits Devices and Systems, vol. 143, pp. 91-96, 1996.

- [23] M. Bhusan and R. W. Newcomb, "Grounding of capacitors in integrated circuits" Electronics Letter, vol. 3, no. 4, pp. 148-149, 1967.

- [24] H. O. Elwan, and A. M. Soliman, "Novel CMOS differential voltage current conveyor and its applications," IEE Proceedings- Circuits Devices and Systems, vol. 144, pp. 195–200, 1997.