# Two DDCC Based Cascadable Voltage-Mode First-Order All-Pass Filters

#### Jitendra Mohan

Department of Electronics & Communication Engineering, Jaypee Institute of Information Technology, Noida (INDIA)

Durg Singh Chauhan

Department of Electrical Engineering,

Institute of Technology, Banaras Hindu University,

Varanasi-221005 (INDIA)

Abstract—In this paper, four new voltage-mode first-order all pass filters are proposed. Each circuit employs two differential difference current conveyors (DDCC) and two passive components with no matching condition. The proposed circuits offer high-input and low-output impedance, low active and passive sensitivities, which is a desirable feature for the voltage-mode systems. Non-ideal analysis and parasitic effect study is also performed. The theoretical results are verified by SPICE simulation.

Keywords— All-pass filter, analog circuits, current conveyor, signal processing.

### I. Introduction

First-order all-pass filters are widely used in analog signal processing to correct the phase shift without changing the amplitude of the applied signal over the frequency range. All-pass filters made from operational amplifier (op-amp) often suffer from limited gain-bandwidth product and slew-rate [1-2].

Recently, current conveyor have been used in implementation of either a current mode or voltage mode filters because of their excellent features such as wide bandwidth, simple circuitry, wider dynamic range, greater linearity, low power consumption as compared to op-amp based voltage-mode filters. Considering these advantages of current mode circuits recently, several voltage mode, all pass filters using various active components have been reported [2-26]. Unfortunately the careful literature review of the previously reported circuits suffer from the following limitations:

- use of excessive passive components. [3-8, 10-13, 15-17, 19]

- use of floating capacitor, which is not desirable for IC implementation. [3, 5, 7-8, 11,19]

Sudhanshu Maheshwari

Department of Electronics Engineering,

Z. H. College of Engineering and Technology,

Aligarh Muslim University, Aligarh-202002 (INDIA)

## Girish Garg

Department of Electronics and Communication Engineering, Jaypee University of Information Technology, Waknaghat, Solan (INDIA)

- requirement of element-matching constraints. [3-8, 10-13, 15, 17, 19]

- Low-input impedance. [4-9, 11, 14, 18, 20-22]

Although the proposed filters in [20-21] employ a single DDCC, one grounded capacitor and one floating resistor. Similarly a single DDCC based all-pass filter with a floating capacitor and grounded resistor was presented in [22]. Such circuits aim is to realize first-order all-pass filter using optimum number of active and passive components rather than offering high-input and/or low-output impedance. The recently reported circuits in [23-25] realize first-order all-pass filters using single FDCCII with grounded components. However it may be noted that a single FDCCII requires more number of transistors than two DDCC together.

The aim of this paper is to propose cascadable voltagemode (VM) first-order all-pass filters by employing two DDCCs, a resistor and a grounded capacitor. The proposed filters offer high-input impedance and low-output impedance. It may be noted that the input impedance should be larger in comparison to the output impedance to avoid loading problem while cascading such circuits to form larger system. Also, the two component based all-pass filter circuits are benefit from the no matching constraint as compared to three or more component based circuits (exceptions are possible if pole and frequency determining components are same). Though a very recently reported filter circuit in [26] employ equal number of active and passive component as the proposed circuit employed but it cannot enjoy the low output impedance at the output terminal. Non-ideal gain and parasitic effects of the DDCCs on the transfer functions of the proposed filters are also investigated.

# II. THE PROPOSED CIRCUIT

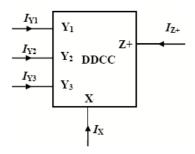

The DDCC whose symbol is shown in Figure 1 [27], is a five terminal active element with the following defining equation

Proc. of the Intl. Conf. on Advances in Electronics, Electrical and Computer Science Engineering — EEC 2012 Edited by Dr. R. K. Singh.

Copyright @ Institute of Research Engineers and Doctors. All rights reserved.

ISBN: 978-981-07-2950-9

$$V_X = V_{Y1} - V_{Y2} + V_{Y3};$$

$I_{Y1} = I_{Y2} = I_{Y3} = 0;$   $I_X = I_{Z+}$  (1)

where the suffixes refer to the respective terminals. The voltage at X-terminal follows the voltage difference and addition of terminal  $Y_1$ ,  $Y_2$ ,  $Y_3$ . The current at terminal Z follow the current at terminal X. The DDCC is characterized by high input impedance at the  $Y_1$ ,  $Y_2$ , and  $Y_3$  terminals, high output impedance at the Z+ terminal and low impedance at the X terminal. DDCC is a useful and versatile active element which

Figure 1. Symbol of DDCC.

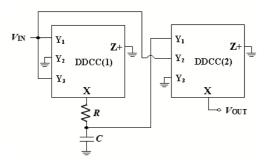

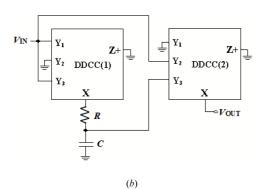

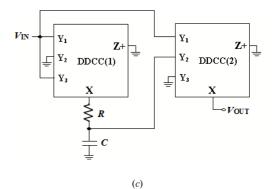

(a)

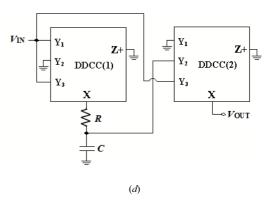

Figure 2. Proposed VM first order all-pass filters (a) Circuit-1; (b) Circuit-2; (c) Circuit-3; and (d) Circuit-4.

has found several applications for analog signal processing [20-22, 28-31].

The proposed VM first order all-pass filters employing two DDCCs, one grounded capacitor and one resistor are shown in Figure 2. Routine analysis of the circuits, gives the following transfer function

$$\frac{V_{OUT}}{V_{IN}} = -\left(\frac{s - (1/CR)}{s + (1/CR)}\right) \tag{2}$$

$$\frac{V_{OUT}}{V_{IN}} = \frac{s - (1/CR)}{s + (1/CR)}$$

(3)

Equation (2) is the transfer function of circuit-1 and -2 with the frequency dependent phase shift  $\Phi = -2 \tan^{-1}(\omega RC)$ , whereas (3) is the transfer function of circuit-3 and -4 with the frequency dependent phase shift  $\Phi = 180^{0}$ -2  $\tan^{-1}(\omega RC)$ . The salient features of the proposed circuits are high input and low output impedance, use of minimum number of passive components and using grounded capacitor that is attractive for integrated circuit implementation.

It is also worth mentioning that four additional new circuits can further be obtained from the proposed circuits by interchanging the resistor (R) with a capacitor (C). However these circuits would employ a capacitor at X terminal, thus degrading high frequency operation.

#### III. NON-IDEAL ANALYSIS AND PARASITIC EFFECT

# A. Non-ideal analysis

Taking the non-idealities of the DDCC into account, the relationship of the terminal voltages and current of DDCC can be rewritten as

where  $\alpha_{kl}$ ,  $\alpha_{k2}$ ,  $\alpha_{k3}$  ( k=1,2) is the voltage transfer gain from Y<sub>1</sub>, Y<sub>2</sub> and Y<sub>3</sub> to the X terminal and  $\beta_{k1}$  is the current transfer gain from X terminal to the Z+ terminal of the k-th DDCC respectively. These transfer gains differ from unity by the voltage and current tracking errors of the DDCC. More specifically,  $\alpha_{kl} = (1 - \varepsilon_{kl})$ ,  $\alpha_{k2} = (1 - \varepsilon_{k2})$ ,  $\alpha_{k3} = (1 - \varepsilon_{k3})$ , and  $\beta_{k1} = (1 - \delta_{kl})$  where,  $\varepsilon_k$  is the voltage transfer error (tracking error) of the k-th DDCC and  $\delta_k$  is the current transfer error (tracking error) of the k-th DDCC. Reanalysis of the circuits in Figure 2 using this description yields the following voltage transfer functions

Circuit-1:

$$\frac{V_{OUT}}{V_{IN}} = -\alpha_{22} \left( \frac{s + \frac{\alpha_{22} - \alpha_{21}(\alpha_{11} + \alpha_{13})}{CR\alpha_{22}}}{s + \frac{1}{CR}} \right)$$

(5)

Circuit-2:

$$\frac{V_{OUT}}{V_{IN}} = -\alpha_{22} \left( \frac{s + \frac{\alpha_{22} - \alpha_{23}(\alpha_{11} + \alpha_{13})}{CR\alpha_{22}}}{\frac{s + \frac{1}{CR}}{CR}} \right)$$

(6)

Circuit-3:

$$\frac{V_{OUT}}{V_{IN}} = \alpha_{21} \left( \frac{s + \frac{\alpha_{21} - \alpha_{22}(\alpha_{11} + \alpha_{13})}{CR\alpha_{21}}}{\frac{s + \frac{1}{CR}}{cR}} \right)$$

(7)

Circuit-4:

$$\frac{V_{OUT}}{V_{IN}} = \alpha_{23} \left( \frac{s + \frac{\alpha_{23} - \alpha_{22}(\alpha_{11} + \alpha_{13})}{CR\alpha_{23}}}{\frac{s + \frac{1}{CR}}{CR}} \right)$$

(8)

From (5) – (8), the pole frequency  $(\omega_0)$  and gain (H) sensitivity to the non-idealities as well as passive components is analyzed and tabulated in Table I.

TABLE I. SENSITIVITY FIGURES

| Sensitivities                                                                                  | Circuits |    |    |    |

|------------------------------------------------------------------------------------------------|----------|----|----|----|

| Sensitivities                                                                                  | -1       | -2 | -3 | -4 |

| $S_{R,C}^{\omega_0}$                                                                           | -1       | -1 | -1 | -1 |

| $S^{\omega_0}_{lpha_{11},lpha_{12},lpha_{13},lpha_{21},lpha_{22},lpha_{23},eta_{11},eta_{21}}$ | 0        | 0  | 0  | 0  |

| $S^H_{lpha_{21}}$                                                                              | 0        | 0  | 1  | 0  |

| $S^H_{lpha_{22}}$                                                                              | 1        | 1  | 0  | 0  |

| $S^H_{lpha_{23}}$                                                                              | 0        | 0  | 0  | 1  |

| $S^H_{lpha_{11},lpha_{12},lpha_{13},eta_{11},eta_{21},R,C}$                                    | 0        | 0  | 0  | 0  |

Table I ensures a good sensitivity performance of the proposed circuits.

### B. Parastic effects

To account for parasitic element, the port X exhibits of low value parasitic serial resistance  $R_X$ , the ports  $Y_1$ ,  $Y_2$  and  $Y_3$  exhibit of high value parasitic resistance  $R_Y$  in parallel with low value capacitor  $C_Y$  and the port Z exhibit of high value parasitic resistance  $R_Z$  in parallel with low value capacitance  $C_Z$  [32]. All the proposed circuits employs resistor at the X terminal of the DDCC, hence the involvement of  $R_X$  is important, beside port Y and Port Z parasitic. A reanalysis of the four circuits, yield the transfer function as

$$\frac{V_{OUT}}{V_{IN}} = k \left( \frac{s - \frac{1}{C(R + R_X)}}{s + \frac{1}{C(R + R_X)}} \right)$$

(9)

where k = +1 for circuit-1 and -2, and k = -1 for circuit-3 and -4.

From (9), the proposed circuit would exhibit a slight deviation in the pole frequency from the designed value but the deviation is small for an integrated DDCC.

# IV. SIMULATION RESULTS

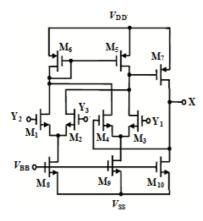

Simulation program with integrated circuit emphasis (SPICE) were carried out to demonstrate the performance of the proposed circuits using 0.5  $\mu$ m CMOS parameters from MOSIS. The CMOS implementation of DDCC is shown in Figure 3 [29], which was modified by eliminating the unused Z+ output terminal from the original DDCC, since it is

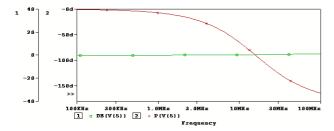

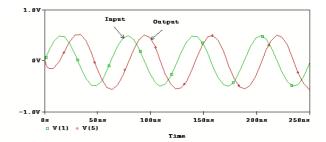

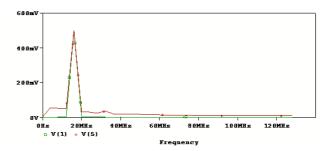

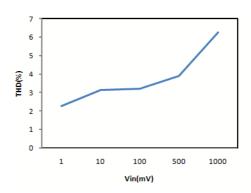

grounded in the proposed circuits (Figure 2). The aspect ratios of the CMOS transistors of the DDCC are listed in Table II. DC supply voltages of  $\pm 2$  V and biasing voltage of  $V_{BB}=-1.15$  V were used . The circuit of Figure 2 was designed with  $R=10~\mathrm{K}\Omega,$  and  $C=1~\mathrm{pF}.$  The gain and phase responses are shown in Figure 4, where a pole frequency of 15.88 MHz is obtained. This is close to the theoretical value of 15.91 MHz. The time domain responses of the proposed circuit-I are shown in Figure 5. The Fourier spectrum of input signal and output signal are shown in Figure 6. Next the signal amplitude is varied from 1mV to 500mV and the Total haromic distrortion (THD) curve is plotted at a frequency of 15.91 MHz is shown in Figure 7.

Figure 3. CMOS implementation of DDCC.

Table II. Aspect ratios of the transistors for the Figure 3.

| Transistors                     | W(µm) | L(µm) |

|---------------------------------|-------|-------|

| $M_1, M_2, M_3, M_4$            | 0.8   | 0.5   |

| M <sub>5</sub> , M <sub>6</sub> | 4     | 0.5   |

| M <sub>7</sub>                  | 10    | 0.5   |

| M <sub>8</sub> , M <sub>9</sub> | 14.4  | 0.5   |

| $M_{10}$                        | 45    | 0.5   |

Figure 4. Simulated Gain and Phase response for circuit-1.

Figure 5. Time domain Input-output responses of Circuit-1

Figure 6. Fourier spectrum of the input and output signal.

Figure 7. THD Variation at output with signal amplitude at 15.91 MHz.

# V. CONCLUSION

In this paper, four new voltage-mode first-order all-pass filters employing two DDCCs are proposed. Each circuit posses high-input impedance and low-output impedance and uses a grounded capacitor, which is suitable for Integrated circuit implementation[33]. The SPICE simulation results of the proposed circuits depict good frequency performance over the existing circuits.

#### REFERENCES

D. Biolek and V. Biolkova, "All-pass filters employing differential Op-Amps. Electronics World, vol. 116, No. 1891, pp. 44 – 45, 2010.

- [2] A. M. Soliman, "Generation of current conveyor based all-pass filters from op-amp based circuits," IEEE Trans. Circuits Syst. II Analog Digital Signal Process., vol. 44, pp. 324–330, 1997.

- [3] M. Higashimura and Y. Fukui," Realization of all-pass networks using a current conveyor," International Journal of Electronics, vol. 65, No. 2, pp. 249–250, 1988.

- [4] O. Cicekoglu, H. Kuntman and S. Berk, "All pass filter using a single current conveyor," Int. J. Electron., vol. 86, No. 8, pp. 947–955, 1999.

- [5] I.A. Khan and S. Maheshwari, "Simple first order all pass sections using a single CCII," Int. J. Electron., vol. 87, No. 3, pp. 303–306, 2000.

- [6] S. Maheshwari and I.A. Khan, "Novel first order all-pass sections using a single CCIII," Int. J. Electron., vol. 88, No. 7, pp. 773–778, 2001.

- [7] A. Toker, S. Özcan, H. Kuntman, and O. Çiçekoğlu, "Supplementary all pass sections with reduced number of passive elements using a single current conveyor," Int. J. Electron, vol. 88, pp. 969–976, 2001.

- [8] N. Pandey and S. K. Paul, "All-pass filters based on CCII- and CCCII-," International Journal of Electronics, vol. 91, No. 8, pp. 485 – 489, 2004.

- [9] S. Maheshwari, "New voltage and current mode all pass sections using current controlled conveyor," Int. J. Electron., vol. 91, No. 12, pp. 735– 743, 2004.

- [10] S. Maheshwari, "High input impedance VM-APSs with grounded passive elements," IET Circuits Devices & Systems, vol. 1, No. 1, pp. 72 – 78, 2007.

- [11] S. Maheshwari, "Voltage-mode all-pass filters including minimum component count circuits," Act. Passive Electron. Compon, pp. 1–5, 2007. (article id 79159)

- [12] S. Maheshwari, "High input impedance voltage-mode first-order all-pass sections," International Journal of Circuit Theory and Applications, vol. 36, No. 4, pp. 511 – 512, 2008.

- [13] B. Metin and O. Cicekoglu, "Component reduced all-pass filter with a grounded capacitor and high input impedance," Int. J. Electron., vol. 96, No. 5, pp. 445–455, 2009.

- [14] D. Biolek and V. Biolkova, "All Pass filters employing one grounded capacitor and one active element," Electron. Letts, vol. 45, No. 16, pp. 807–808, 2009.

- [15] B. Metin and K. Pal, "Cascadable all-pass filter with a single DO-CCII and a grounded capacitor," Analog Integrated Circuits and Signal Processing, vol. 61, No. 3, pp. 259 – 263, 2009.

- [16] T. Tsukutani, H. Tsunetsugu, Y. Sumi, and N. Yabuki, "Electronically tunable first order all pass circuit employing DVCC and OTA," Int. J. Electron, vol. 97, No. 3, pp. 285–293, 2010.

- [17] S. Minaei and E. Yuce, "Unity/variable-gain voltage-mode/current-mode first-order all-pass filters using single Dual-X second-generation current conveyor," IETE J. Res., vol. 56, pp. 305–312, 2010.

- [18] K. Pal and C. Psychalinos, "All-pass filters realized using the current controlled CCII with intrinsic negative resistance," Int. J. Electron., vol. 97, No. 5, pp. 491–498, 2010.

- [19] S. Maheshwari and B. Chaturvedi "High-input low-output impedance all-pass filters using one active element." IET Circuits Devices Syst., vol. 6, No. 2, pp. 103–110, 2012.

- [20] J.W. Horng, C.L. Hou, C.M. Chang, Y.T. Lin, I.C. Shiu and W.Y. Chiu, "First order all pass filter and sinusoidal oscillator using DDCCs," Int. J. Electron, vol. 93, No. 7, pp. 457–466, 2006.

- [21] H. P. Chen and K. H. Wu, "Grounded Capacitor First Order Filter Using Minimum Components," IEICE Trans actions on Fundamentals of Electronics, vol. E89-A, No. 12 pp. 3730-1, 2006.

- [22] M.A. Ibrahim and H. Kuntman, O. Cicekoglu, "First order all pass filter canonical in the number of resistors and capacitors employing a Single DDCC," Circuits Syst. Signal Process, vol. 22, No. 5, pp. 525–536, 2003.

- [23] S. Maheshwari, J. Mohan and D.S. Chauhan, "Voltage mode cascadable all pass sections with two grounded passive components and one active element," IET Circuits Devices Syst., vol. 4, No. 2, pp. 113–122, 2010.

- [24] S. Maheshwari, J. Mohan and D.S. Chauhan, "Voltage mode cascadable all-pass sections using single active element and grounded passive components," Circuits System, vol. 1, pp. 5–11, 2010.

- [25] S. Maheshwari, J. Mohan and D. S. Chauhan "High input impedance VM-APSs with grounded passive components and one active element" International Conference on Advances in Recent Technologies in Communication and Computing (ARTCOM), pp.324-329, 2009.

- [26] S. Minaei and E. Yuce, "Novel voltage-mode all-pass filter based on using DVCCs," Circuits, Systems and Signal Processing, vol. 29, No. 3, pp. 391 – 402, 2010.

- [27] W. Chiu, S. I. Liu, H. W. Tsao and J. J. Chen, "CMOS differential difference current conveyors and their applications." *IEE Proceedings*-Circuits Devices and Systems, vol. 143, pp. 91–96, 1996.

- [28] M. A. Ibrahim and H. Kuntman, "High linearity CMOS differential difference current conveyor (DDCC)." In The 14th International Conference on Microelectronics (ICM 2002). Beirut (Lebanon), pp. 6-9, 2002.

- [29] H. O., Elwan and A. M. Soliman, "Novel CMOS differential voltage current conveyor and its applications." IEE Proceedings, Part G, vol. 144, pp. 195–200, 1997.

- [30] S. Maheshwari, J. Mohan and D. S. Chauhan, "Cascadable all-pass and notch filter configurations employing two plus-type DDCCs," Journal of Circuits, Systems, and Computers, vol. 20, pp. 329-347, 2011.

- [31] H. P. Chen and K. H. Wu, "Single DDCC-based voltage-mode multifunction filter." IEICE Transactions on Fundamentals of Electronics Communications and Computer Sciences, vol. E90-A, p. 2029–2031, 2007.

- [32] E. Tlelo-Cuautle, C. Sanchez-Lopez and D. Moro-Frias," Symbolic analysis of (MO)(I)CCI(II)(III)-based analog circuits" International Journal of Circuit Theory and Applications, vol. 38, No. 6, pp. 649–659, 2010.

- [33] M. Bhushan and R. W. Newcomb, "Grounding of capacitors in integrated circuits." *Electronics Letters*, vol. 3, pp. 148–149, 1967.