# A New Generalized Asymmetrical Cascade Multilevel Inverter Topology with Reduced Power Electronic Switches and Dc Sources

G. Sridhar

P. Satishkumar

M. Sushama

Abstract-- In the past few years the demand for the achievements in development of multilevel inverter topologies has been increasing a lot. Recently presented topologies accomplish higher number output voltage levels with few number of switches, DC voltage sources, and reduced voltage stress across switches, with fewer losses as compared with conventional topologies. Minimization of switches and dc voltage sources reduces complexity, cost size and improves the overall performance. These benefits are proposed in this paper with a new topology of asymmetrical cascaded multilevel inverter. This developed structure provides reduced number of controlled switches, DC sources, as compared with conventional and presented topologies in the literature so far.

The proposed asymmetrical topology generates seven voltage levels with eight switches only. Furthermore reduction in voltage stress across the switches can be attained. Phase Opposition Disposition (POD) is adopted for generating switching pulses. The proposed topology is simulated using MATLAB/SIMULINK and results have been validated experimentally.

Keywords: Asymmetrical multilevel inverter, reduction of Switches, dc voltage sources, POD.

#### I. Introduction:

Introduction of multilevel inverter was done in 1975, since its introduction the demand in the field of DC/AC power conversion and associated applications has been increasing [1]. In the recent day MLI is gaining much fame in the field of Dc/AC conversion due to less THD, better power quality and good electromagnetic compatibility.

Even after having many merits MLI has few demerits that is to maximize output voltage levels semiconductor switch requirements with peripheral devices like protection circuits, gate driver circuits used extensively .Due to more device count the overall system becomes expensive ,stupendous

**G.Sridhar**

Jyothishmathi Institute of Technology and Science, karimnagar, Telangana State India

P.Satishkumar Osmania University, India

M.Sushama Jawaharlal technological University Hyderabad, India and complicated and minimizes the quality and competency of the converter[2-11].

MLI are grouped into Cascaded H Bridge, Flying capacitor and Neutral point Clamped traditionally. In the recent past most of the published articles showed the study on NPC, FC and CHB topologies regarding their merits and demerits [12]. Among MLI topologies CHB is popular due its coherence and easy operation but the limitation of the topology is requirement of isolated dc power supplies [13]. CHB is arranged as asymmetric and symmetric configuration based on magnitude of the dc voltage sources. If V1=V2=V3... is symmetric vice versa. For the same number of power switches the symmetric configuration of CHB generates lesser number of voltage levels as compared with asymmetric configuration.

A combination of unidirectional and bidirectional switches of different ratings have been utilized with reduced device count have been offered by the large number of topologies and control schemes in the recent past [12-22]. The requirement of large number of bidirectional switches is a major issue in asymmetrical topologies. An effort has been attempted to reduce bidirectional switches in asymmetrical topology by proposing a new topology in this paper. The cost of the symmetrical topology MLI is less due to less different dc voltage sources but the major problem is its modularity [22]. The topologies presented in [21-22], has the limitation that all the voltage levels (series/parallel) cannot be ascertained with the suggested algorithms.

In [21] topology of MLI constituted many bidirectional switches is presented. Owing to bidirectional switches, voltage stress over the switches and number of devices is more.

In this paper new topology of asymmetrical MLI is proposed. The proposed topology is capable of producing 7 output voltage levels by utilizing 8 controlled switches.. Experimental results as well as Simulation results are described for 7-level multi level inverter to verify the proposed topology.

# II. Proposed Multilevel Inverter Topologies:

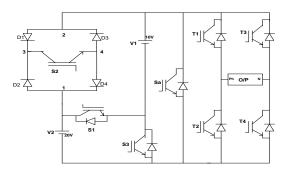

The proposed topology shown in Figure 1. The topology is composed with two dc voltage sources V1 and V2 along with polarity generation circuit ,it consist high frequency switches and should withstand to high switching frequency to produce required voltage levels and polarity conversion circuit, is responsible for the conversion of the polarity of the output voltage, is the low frequency part operating at line frequency. In polarity generation four diodes D1-D4 are connected in anti parallel to avoid dead short circuit across the switches and dc voltage sources. When DC voltage sources unequal  $(V1 \neq V2)$ can be called as asymmetrical otherwise symmetrical. The presented topology can produce seven level output voltage with eight controlled switches only. Batteries, capacitors and isolated dc voltage supplies can be used as dc voltage sources in this topology. When ac voltage sources are available using rectifiers and isolated transformers multiple dc voltage sources can be produced. The problem of voltage balancing is eliminated by employing fixed dc voltage source. The proposed topology can be easily extended to three phase system.

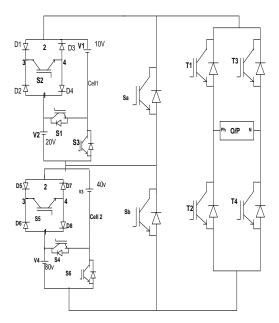

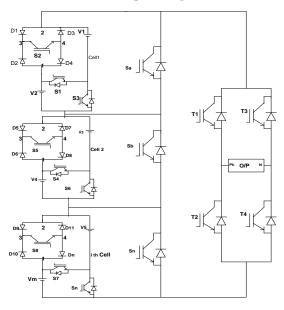

When S3 switch is ON and S1, S2 are OFF dc voltage source V1 is connected in parallel to polarity generation circuit in the output, when S2 switch is ON dc voltage source V2 is connected to polarity generation circuit in the output. When switch S1 is ON the dc voltage sources are connected in series (V1+V2 voltage will appear across the output of polarity generation circuit) by flowing the current through S1. When switches S1, S2 and S3 are OFF and Sa is ON Zero voltage will appear across polarity generation circuit. Thus by using the above switching sequence four output voltage levels are achieved differently can be observes from Figure 4. The arrangement of the basic cell for 16level output voltage shown in Figure 2. The generalized structure of the proposed topology shown in figure3. To avoid the short circuit of the switches four diodes are connected in parallel to switch s2. The switching states of the proposed MLI with particular combination of the switches and corresponding voltage levels for 7level summarized in TableI

Figure 1. Proposed Topology

Figure 2: Arrangement of Basic cell of the proposed Topology for 16Level Output voltage

Figure 3. Generalized Structure of the proposed single Phase Topology

Table I: Switching states of the Proposed Topology shown in Figure 1

| shown in Figure1 |                   |                |  |

|------------------|-------------------|----------------|--|

| S.No             | ON State Switches | Output Voltage |  |

| 1                | Sa                | 0              |  |

| 2                | S3                | V1             |  |

| 3                | S2,D2,D3          | V2             |  |

| 4                | S1                | V1+V2          |  |

Proc. of The Sixth Intl. Conf. On Advances In Computing, Control And Networking - ACCN 2017 Copyright © Institute of Research Engineers and Doctors, USA .All rights reserved. ISBN: 978-1-63248-118-4 doi: 10.15224/978-1-63248-118-4-19

It is important to mention here that the power switches for the polarity generation part need to have a minimum voltage rating equal to the operating voltage of the MLI. Hence the H Bridge is used as polarity conversion circuit and switches of H Bridge must able to tolerate the voltage equal to rated output voltage of the MLI

These four switches of H Bridge turn ON and OFF once during a fundamental cycle, hence these four switches restrict for the application of high voltage. As the proposed topology facilitates cascade connection the basic cells that solve the above problem and reduce the voltage stress across the switches.

In the presented topology [16], while operating polarity generation circuit switches, the switches may undergo short circuit with connected dc voltage sources due to forward biased diodes, this makes huge circulating current will flow through the switches this leads to burning of the high frequency switches which increases the cost of the inverter and reduces the reliability.

This problem can be overcome by the proposed topology. The anti parallel diodes connected across switch does not provide the closed path for the current to circulate through the high frequency switches. It is clearly observed from the Figure 1 when switch S2 is OFF, either switch S1 or S3 is conducting D2,D3 or D1,D4are in reverse biased condition that will not allow the current through it.

The values of the dc voltage sources employed in the asymmetrical MLI are assumed differently in the different cells such that maximum output voltage levels can be produced using lesser switching devices.

In asymmetrical topology the dc voltage sources values are unequal. Based on above condition the below equations are obtained for 'm' basic units

$$Nsource = 2m \tag{1}$$

$$Nswitch = 2Nsource + 4$$

(2)

$$Nlevel = 2^{Nsource}$$

(3)

Nsource, Nswitch, Nlevel are the number of dc voltage sources, number of switches and number of output voltage levels respectively

The magnitude of the dc voltage sources can be selected using following equation, For the  $m^{th}$  basic unit, The value of the  $n_{th}$  dc voltage source in  $m^{th}$  basic unit

$$Vdcm, n = 2^{(n-1)}Vdc (4)$$

For basic unit 1 consisting of 2 voltage sources Vdc1&Vdc2 The maximum output voltage is obtained by the m<sup>th</sup> Unit of the proposed topology can be determined as follows;

The Maxmum Output Voltage:

$$Vo \max = (2^{2m} - 1)Vdc \tag{5}$$

In designing the cascaded Multilevel Inverters, it is important to consider the standing voltage of the power electronic switches. It is defined as the maximum operating voltage that present across switches during each mode of operation.

The standing voltage of the switches in m<sup>th</sup> cascaded multilevel inverter basic unit (Vsm) in asymmetrical condition can be written

$$Vsm = 4(V1,1+V1,2+V2,3+V2,4+...Vnm)$$

(6)

From the equation (4) V1,1, V1,2...etc can be written as

V1,1=Vdc: V1,2=2Vdc: V2,3=4Vdc: 2,4=8Vdc....

$$Vsm = 4(Vd + 2Vd + 4Vd + 8Vd + ....)$$

(7)

Therefore the sum of the standing voltage of the switches in m basic units consisting of n dc voltage sources equal to

$$Vsm = 4\sum_{m=1}^{n} Vmn$$

(8)

The asymmetrical topology consisting of n dc voltage sources the total standing voltage equal to

$$Vsn = 2 * \sum_{n=1}^{j} 2^{n-1} Vdc$$

(9)

#### **III. Modulation Schemes:**

Carrier based multi carrier modulations methods namely phase disposition (PD), Phase Opposition Disposition (POD), Alternative Phase Opposition Disposition (APOD) have been employed widely for switching of multilevel inverters due to their less computational requirements, flexibility and simplicity. Alternative Phase Opposition Disposition (APOD) PWM technique is employed for generating switching pulses

# Alternative Phase Opposition Disposition (APOD) PWM Method:

In this method each carrier is phase shifted by 180 degrees from its adjacent.

# **IV. Simulation Results:**

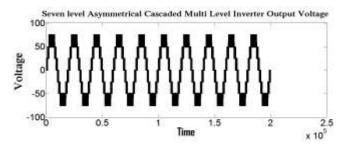

The required switching pulses in proposed topology is generated using PD,POD and APOD pulse width modulation techniques for 7 level asymmetrical topology and simulated using MATLAB/Simulink and developed prototype hardware model .

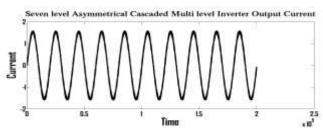

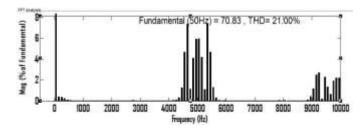

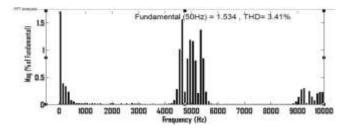

The simulated results of output voltage and current of the proposed seven level asymmetrical MLI using Alternative phase opposition disposition (APOD) PWM shown in Figure 4. Figure 5. It can be observed that the output voltage and current is nearly sinusoidal. The FFT analysis of the voltage and current wave forms of the above PWM techniques shown in Figure 6, Figure 7.

Figure 4. Output Voltage of 7level Asymmetrical MLI of proposed topology using APODPWM

Figure 5. Output Current of 7level Asymmetrical MLI of proposed topology using APODPWM

Figure 6. Output Voltage THD of 7level Asymmetrical MLI of proposed topology using APOD PWM

Figure 7. Output Current THD of 7level Asymmetrical MLI of proposed topology using APOD PWM

# V. Experimental Results:

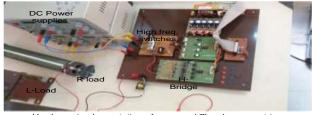

To approve and ensure the concept and feasibility of the proposed asymmetrical topology experimental setup has been prepared for 7 levels of output voltage and validated experimentally with R-L load (R=50 $\Omega$  and L=55mH) shown in Figure8. Switching pulses for H Bridge (T1 & T2) , for high frequency switches (S1, S2&S3) are generated using Alternative Phase Opposition Disposition (APOD) pulse width modulation technique.

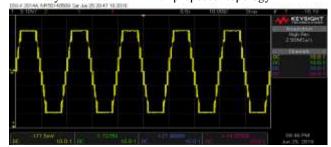

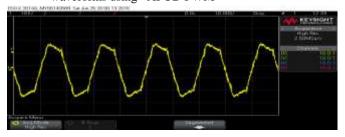

The experimentally obtained voltage and current wave forms of the proposed 7level asymmetrical topology using APOD PWM technique are shown in Figure 9, Figure 10.

Hardware implementation of proposed 7level asymmetric MLI

Figure 8. Experimental circuit of Proposed 7 level asymmetrical MLI with proposed topology

Figure 9. Proposed 7 level asymmetrical topology Voltage waveforms using APOD PWM

Figure 10. Proposed 7level asymmetrical topology Curren waveforms using APOD PWM

**TableII. Comparison of Total Harmonic Distortion**

| Simulation   | $V_{THD}$ | I <sub>THD</sub> |

|--------------|-----------|------------------|

| Simulation   | 21.07     | 3.42             |

| Experimental | 4.01      | 8.33             |

### **Conclusion:**

In this paper a new generalized topology for asymmetrical multilevel inverter that works on the base of the series connection of the dc voltage sources was proposed. In the proposed topology the basic cell is connected in such way that the maximum number of voltage levels is attained. Algorithms were proposed for the magnitude of the dc voltage sources, number of voltage levels attained, number of switches required and maximum value of the output voltages. A 7level asymmetrical MLI prototype hard ware implemented to verify the ability of the proposed topology.

#### Acknowledgment

We thank the University Grants Commission (UGC), New Delhi for providing the Major Research Project to Dr.P.Satishkumar to carry out the research in the area of Cascaded multi-level inverters. We also thank the Principal and Head of the department, University College of Engineering, Osmania University for their encouragement and support and permitted me to utilize equipment.

#### References

- Shivamprakasham gautham, LalithKumar, Shubhrata gupta: Hybrid Topology of symmetrical multilevel inverter using less number of devices.IET Power Electron.8 (11),2125-2135(2015)

- [2] Rodriguez J,S.Bernet,B.Wu,J.OKouro: Multilevel voltage source converter topologies for industrial medium voltage drives.IEEE Trans.Ind.Electron,54(6),2930-2945(2007)

- [3] De,S,Benerjee,D.Sivakumar,K.Gopakumar K,. Ramchand R, Patil C:Multilevel Inverters for low power applications IET Power Electron4(4),394-392(2011)

- [4] palanivel,P.,Dash .S.S: Analysis of THD and output voltage performance for cascade multilevel inverter using carrier pulse width modulation technique. IET Power Electron4(8)951-958(2011)

- [5] Gupta, K K, Jain. S: Topology for multi level inverters to attain maximum number of levels from given dc sources. IET Power Electron, 5(4)435-446(2012)

- [6] Banaei M.R,Khounjahan H,Salary E:Single source cascaded transformers multilevel inverter with reduced number of switches. IET Power Electron, 5(9),1748-1753(2012)

- [7] sadigh,A.K,Dargahi,V,Abarzadeh,M,Dargahi,S:Reduced DC voltage source flying capacitor multi cell multilevel inverter analysis and implementation, IET Power Electron,7(2),439-450 (2014)

- [8] Al-Judi A,Nowicki E,Cascading of diode bypassed transistor voltage source units in multilevel inverters, IET Power Electron,6(3),554-560(2013)

- [9] Ajami.A, Oskuee M.R.J, Mokhberdoran, V.d.Bossche: Developed cascaded multilevel inverter topology to minimize the number of circuit devices and voltage stresses of switches; IET Power Electron ,6(3),459-466(2014)

- [10] Shalchi A.R, Nazarpour D, Hosseni S.H, Sabahi M: New hybrid structure for multi level inverter with fewer number of components for high voltage levels, IET Power Electron 7(1),96-104 (2014)

- [11] Guptak.K,Jain.S:Comprhensive review of a recently proposed multi level inverter, IET Power Electron7(3),467-479(2014)

- [12] OdejC.J,Nandi D.B.N: Single phase 9level hybridized cascade multi level inverter, IET Power Electron6(3)468-477(2013)

- [13] Nefaji E,Yatim A.H.M: Design and implementation of new multilevel inverter topology IEEE Ind.. Electron ,59(11),4148-4154(2012).

- [14] GuptaK.K.,Jain S.S: A novel multilevel inverter based on switched dc sources, IEEE Ind.Electron,61(7),3269-3278(2014).

- [15] Dixon J,Moran L: High level multi step inverter optimization using a minimum number of power transistor,IEEE Trans.Power electron 21(2),330-337(2006)

- [16] HinagoY,Koizumi: A single phase multi level inverter using switched series/parallel DC voltage sources, IEEE Trans. Ind. Electron,57(8) ,2643-2650(2010)

- [17] Ebrahimi.J,Babaei,Gharehpetin G.B: A new multi level converter topology with reduced number of power electronic components, , IEEE Trans. Ind. Electron,59(2),655-667(2012)

- [18] Mokhberdorn.A,Ajami.A:Symmetric and asymmetric design and implementation of new cascade multi level inverter topology , IEEE Trans. Power Electron,29(12),6712-6724(2014)

- [19] Chattopadhyay,S.K,Chakraborthy.C:A new multilevel inverter topology with self balancing level doubling network, IEEE Trans. Ind. Electron,61(9),4622-4631(2014)

- [20] Babaei E, Laali, S, Alilu,S:Cascade multilevel inverter with series connection novel H bridge basic units, IEEE Trans. Ind. Electron,61(12),6664-6671(2014)

- [21] Babaei.E: A cascade multi level inverter topology with reduced number of switches, IEEE Trans. Power Electron ,23(6),2657-2664(2008)

Zambra D A,Reeh C,Pinheiro J.R: A comparative analysis between the symmetric and the hybrid asymmetric nnine level series connected H bridge cells inverter: European Conf.On power electronics and applications, 2-5 Sept.2007 ,pp1-10

**About Author (s):**

G.Sridhar was born in Karimnagar; Telangana India in 1978.he obtained the B.Tech degree in Electrical Engineering from university of madras in 2000 and M.Tech in power systems with emphasis on high voltage engineering in 2005from JNTU Kakinada. He is pursing PhD degree in the area of multilevel inverter. He is working as associate professor in the department of Electrical Engineering. Jyothishmathi Institute of Technology and Science, karimnagar. His research interest includes power electronics and multilevel inverters and has 16 years of teaching experience

P. Satish Kumar was born in Karimnagar, Andhra Pradesh, INDIA in 1974. He obtained the B.Tech. degree in Electrical and Electronics Engineering from JNTU College of Engineering, Kakinada, INDIA in 1996. He obtained M.Tech degree in Power Electronics in 2003 and Ph.D. in 2011 from JNTUH, Hyderabad. He has more than 17 years of teaching experience and at present he is an Assistant Professor in the Department of Electrical Engineering, University College of Engineering, Osmania University, Hyderabad, INDIA. His research interests include Power Electronics, Special Machines, Drives and Multilevel inverters

Dr.M.Sushama was born in 1973, in Nalgonda district, Telangana state. India. Obtained B.Tech degree in 1993 and M.Tech degree in 2003, specialization in Electrical Power Systems from JNTU, INDIA. She obtained her Ph.D. from JNTU Hyderabad, in 2009 in the area of "Power Quality" using Wavelet Transforms. She has more than 19 years of teaching experience and at present she is working as head and professor in the department of electrical and electronics engineering, JNTUH, Hyderabad, India. Her research interests includes green energy, power systems, power electron power quality and harma

DIGITAL LIBRARY