# Fabrication of high-performance Ge-MOS structure using TiO<sub>2</sub> inserted layer in gate insulator for high speed switching device

[ Kenichiro Toyoda, Daichi Hasegawa, Ryuichiro Watanabe, Yoshitaka Iwazaki, Tomo Ueno ]

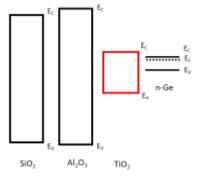

Abstract— In recent years, combination of high mobility (Highu) materials and high dielectric constant (High-k) insulating films has attracted attention as a technique for future switching devices such as high speed switching, low voltage operation and so on. Using a Ge substrate having higher carrier mobility than that of Si as a high-µ material, it is expected that the operation speed of the device will be increased. On the other hand, it is necessary to introduce a high-k material, for example HfO2, Al<sub>2</sub>O<sub>3</sub>, in order to increase the capacitance value while maintaining the insulating film thickness, and the like have been studied so far. However, it is difficult to obtain good interface characteristics by direct deposition of HfO2 or Al2O3 on Ge substrates. In this study, we tried to introduce another high dielectric constant material TiO2, whose dielectric constant value is approximately 15 times higher(~60) than that of SiO<sub>2</sub>(~3.9). However, the energy band gap of TiO<sub>2</sub> is very small at 3.2 [eV], and  $E_C$  (conduction band edge) of  $TiO_2$  is close to that of Si and Ge. Therefore, the use of only TiO2 film itself as insulating film would be difficult because of large leakage current. Hence, we have considered a stacked structure with Al<sub>2</sub>O<sub>3</sub>, which has a large band gap (8.8 [eV]) and has a large band offset with Si and Ge. It scales the increase in capacitance while maintaining the film thickness and suppresses leakage current. In this study, high performance Ge-MOS was realized with Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>/Ge structure.

Keywords—Switching device, Ge-MOS, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>

### . Introduction

# A. The structure of MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) and its issue for future high speed switching operation

In recent years, the performance of digital electronic devices has been improved due to the development of MOSFETs, which are electrical switching elements for logic circuits. The electrical properties can be controlled by the applied voltage to the metal layer, that is so called Gate region for the circuit technology.

- · Kenichiro Toyoda

- · Tokyo univ. of agri. and tech.

- Japan

Since high speed operation such as small turn-on and turn-off time is required for high speed switching devices, applying high carrier mobility materials at the S:Semiconductor region as well as high dielectric constant materials at the O:Oxide layer has been expected for future switching devices.

In this study, Ge was used for the semiconductor substrate of the MOSFET and TiO<sub>2</sub> was used for the insulating film. Since Ge has higher carrier mobility than conventional Si, it can be expected to increase the switching speed of the device without reducing the length of the channel between the source and the drain. In addition, TiO2 has a relative dielectric constant of approximately ~60, which is much higher than that of conventional SiO<sub>2</sub>, or Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> of represented high-k materials. It is considered that the use of high-k material makes it possible to reduce power consumption while maintaining the insulating film thickness because the operation voltage would be decreased. However, TiO<sub>2</sub> has disadvantages from the view point of insulating properties. Figure. 1 and Table 1 show the energy band diagram and the relative dielectric constant of each material, respectively. Since the band gap of TiO<sub>2</sub> is very narrow of 3.2 [eV] and there is almost no band offset from bottom E<sub>C</sub> (conduction band edge) of TiO<sub>2</sub> and that of Ge, it can be expected that the insulation property is very poor. Therefore, a stacked structure with Al<sub>2</sub>O<sub>3</sub>, which is a high-k material having a wide band gap of 8.8 [eV] and having large band offset with E<sub>C</sub> of Ge. It is considered that by forming a stacked structure of Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> as the insulating layer, it is possible to suppress the leakage current while taking advantage of TiO<sub>2</sub>.

In this work, to fabricate the  $Al_2O_3/TiO_2$  stacked structure directly onto Ge substrate, the technique so-called reactive sputtering method has been used. The reactive sputtering method is capable of easily depositing a material with a high deposition rate at room temperature, but it is difficult to obtain good interface characteristics with Ge substrate. As a conventional improvement technique, there is a method of inserting a  $GeO_2$  film as an interface layer to eliminate the influence of sputtering on the interface. However, in this method, since the relative dielectric constant of  $GeO_2$  is low (~5) and the total thickness of the insulating film is large, it is difficult to utilize the merit of  $TiO_2$ . Therefore, in this experiment, we performed annealing in  $N_2$  atmosphere, and also verified whether good interface characteristics can be obtained without inserting a  $GeO_2$  film.

Fig.1 Energy band diagram of each materials

Table.1 Relative dielectric constant and band gap of each materials

| Material                       | E,   | E <sub>g</sub> [eV] |

|--------------------------------|------|---------------------|

| SiO <sub>2</sub>               | 3.9  | 9.0                 |

| Al <sub>2</sub> O <sub>3</sub> | 8~10 | 8.8                 |

| TiO <sub>2</sub>               | 60   | 3.3                 |

## п. Experimental

The n-type Ge (100) substrate was subjected to chemical solution dip to remove a native oxide film, thereby fabricating four types of samples. Detailed experimental conditions are shown in Table 2.

Sample No.1: Deposit TiO<sub>2</sub> using reactive sputtering

Sample No.2: N<sub>2</sub> annealing for Sample No.1

Sample No.3: Deposit  $\text{TiO}_2$  using reactive sputtering, then

deposit Al<sub>2</sub>O<sub>3</sub>

Sample No.4: N<sub>2</sub> annealing for Sample No.3

After the preparation of each sample, an Al electrode was formed by vacuum evaporation, and C-V measurement and J- $\bar{\rm E}$  measurement were performed to evaluate electrical characteristics. (The C-V measurement circuit diagram is shown in figure. 2.)

Table.2 Detailed experimental conditions

Fig.2 Circuit for C-V measurement

#### ш. Results and discussion

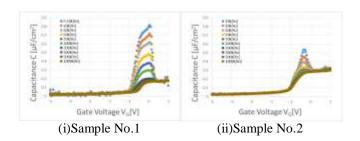

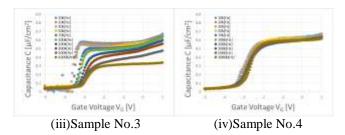

Fig.3 C-V measurement results

#### A. C-V characteristics

Figure. 3 shows the C-V measurement results of each sample (i)~(iv). The measurements have been performed under each of the DC gate voltage(V<sub>G</sub>) from 1 [V] to -5 [V], adding the AC voltage(dV) with a frequency(f) from 10 [kHz] to 1000 [kHz] to the gate. The capacitance value(C) could be obtained by the calculation of  $d \int i(t)dt/dt$ . From the C-V measurement results, the characteristics of the insulating film-semiconductor interface have been able to evaluated. Generally speaking, the existence of frequency dispersion means that there exist a lot of defects at the insulator/semiconductor interface. From the results of figure 3 (i) and 3 (ii), even though the C-V curves both of Sample No. 1 and Sample No. 2 have frequency dispersion, they have been somewhat improved by N2 annealing shown in figure 3 (ii). However, in both cases, the capacitance value decreased at the positive bias side. From the results of figure 3 (iii) and 3 (iv), on the other hand, the frequency dispersion of Sample No. 4 shown in figure 3 (iv) was significantly suppressed by N<sub>2</sub> annealing compared with Sample No.3. In addition, there were no decrease of the capacitance value on the positive bias side in Sample No.3 and Sample No.4. Therefore, we can conclude the following results. (1)It was found that N2 annealing had some effect of improving the interface characteristics even in the TiO2 / Ge structure, which is formed by the direct deposition using reactive sputtering method on Ge substrates. (2) The decrease of the capacitance value on the positive bias side for TiO2 / Ge structure w/ and w/o N<sub>2</sub> annealing shown in figure 3 (i) and 3 (ii) might be due to the large leakage current discussed later. The use of only TiO<sub>2</sub> layer as the insulator would have insufficient insulating property. (3)For Al<sub>2</sub>O<sub>3</sub>/ TiO<sub>2</sub> / Ge structure, on the other hand, N2 annealing also had effect of improving the interface characteristics. In addition, the C-V characteristics shown in figure 3 (iv) reveals the fact that the annealed  $Al_2O_3/\ TiO_2$  / Ge structure have had the ideal interface property because of few frequency dispersion.(4) Using Al<sub>2</sub>O<sub>3</sub> layer on the TiO<sub>2</sub> / Ge structure w/ and w/o N<sub>2</sub>

annealing shown in figure 3 (iii) and 3 (iv), there were no decreases of the capacitance value on the positive bias side. The addition of  $Al_2O_3$  layer on the  $TiO_2$  / Ge structure might cause the suppression of leakage current discussed later. Therefore, stacked structure of  $Al_2O_3/TiO_2$  with  $N_2$  annealing as the insulating layer could suppress the leakage current as well as improve the interface properties.

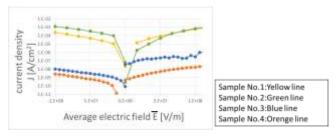

## B. J-E characteristics

Fig. 4 shows the  $J-\overline{E}$  measurement results of each sample No.1~4. The vertical axis represents the current density(J[A/cm<sup>2</sup>]), and the horizontal axis represents the average electric field( $\overline{E}[V/m]$ ) for the whole insulating film.(Actually, for Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> stacked insulating film, applied electric field in each layer would be different because it depends on the dielectric constant value of each layer.) For Sample No. 1 and Sample No. 2, the leakage current were very large and there was almost no change of the leakage current level after the N<sub>2</sub> annealing. On the other hand, for Sample No. 3 and Sample No. 4, the leakage current were significantly suppressed by addition of Al<sub>2</sub>O<sub>3</sub> layer on the TiO<sub>2</sub>/Ge structure. Furthermore, the suppression effect of leakage current was somewhat increased by N<sub>2</sub> annealing. As can be seen from the energy band diagram shown in figure 1, the leakage current cannot be suppressed only by TiO<sub>2</sub> even with N<sub>2</sub> annealing. It can be improved by forming a stacked structure with Al<sub>2</sub>O<sub>3</sub>, and it is considered that the film quality of Al<sub>2</sub>O<sub>3</sub> is improved by N<sub>2</sub> annealing.

Fig.4 J-E measurement results

#### **IV.** Conclusion

We have attempted the use of TiO2 as insulating film on Ge substrates for high speed switching devices. Although good interface characteristics cannot be obtained by direct deposition of TiO2 using reactive sputtering method, N2 annealing causes some improvement with the decreasing the number of defects at the insulator/semiconductor interface. The effect is further enhanced by forming a stacked structure with Al<sub>2</sub>O<sub>3</sub> layer, and Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub>/Ge structure with N<sub>2</sub> annealing shows the ideal interface property. Further, as can be seen from the energy band diagram, the use of only TiO<sub>2</sub> as insulating layer has no effect of suppressing leakage current, and higher leakage level have still hold even after N<sub>2</sub> annealing. However, it can be suppressed by forming a stacked structure with Al<sub>2</sub>O<sub>3</sub>, and by performing N<sub>2</sub> annealing, the film quality of Al<sub>2</sub>O<sub>3</sub> is improved, and the suppression effect is further increased.

#### References

- Shankar Swaminathan, Michael Shandalov, Yasuhiro Oshima, and Paul C. McIntyre "Bilayer metal oxide gate insulators for scaled Gechannel metal-oxide-semiconductor devices" APPLIED PHYSICS LETTERS 96, 082904. (2010)

- [2] C.K. Maiti, S.K. samanta, G.K. Dalapati, S.K. Nandi, S.Chatterjee, "Electricl characterization of TiO<sub>2</sub> gate oxides on strained-Si" Microelectronic Engineering 72 (2004) 253-256.

About Author (s):

• Master Course, Department of Electrical and Electronic Engineering, graduate school of TUAT(Tokyo univ. of agri. and tech, Japan)